ジッパーノイズもポップノイズもなし!

ADCハイブリッド・ゲイン制御で、ポップフリーのマイク・プリアンプ・ゲイン変更をスムーズに実現する方法

この記事では、Cirrus Logic製CS530xPプロ仕様オーディオADCファミリーの新しいハイブリッド・ゲイン制御 (HGC) 機能、およびデジタル制御によるマイク・プリアンプ・ゲインを変更する際に、ノイズ問題を解消する方法について説明します。これは、プロ仕様オーディオ機器の設計者にとって長年の課題でした。このソリューションでは、制御を組み込んだADCのほか、ゼロ交差検出と正確な同期デジタルゲイン制御によって、従来のポテンショメータのような感覚で、可聴ポップやジッパーノイズの発生しない、微細な解像度のマイク・プリアンプ・ゲイン制御が可能になります。

Cirrus Logic製CS530xPファミリーのプロ仕様オーディオADCハイブリッド・ゲイン制御 (HGC) 機能を使用すると、デジタル制御マイク・プリアンプのゲイン変更時に発生するポップノイズとジッパーノイズを簡単に解消できます。このポップノイズとジッパーノイズは、プロ仕様オーディオ機器の設計者にとって長年の課題です。従来のポテンショメータのような感覚で、可聴ポップやジッパーノイズの発生しない、微細な解像度のマイク・プリアンプ・ゲイン制御を実現する既存のソリューションは、多くの場合、高価で複雑になります。HGCは、マイク・プリアンプのゲイン制御をADCに統合し、ゼロ交差検出と正確な同期デジタル・ゲイン制御と併せて、この問題を解決します。HGCは、既存のマイク・プリアンプ設計を保持し、ハードウェアとソフトウェアの両方を簡素化しながら、プロ仕様オーディオ製品の設計者がスムーズなポップフリーのゲイン制御を簡単に実現できるようにします。

マイク・プリアンプのデジタル・ゲイン制御

従来、ミキシング・コンソールなどのアナログのプロ仕様オーディオ製品のマイク・プリアンプ・ゲインは、ポテンショメータによって制御されていました。デジタル・オーディオ・ミキシング・コンソールの登場により、マイク・プリアンプ・ゲインをデジタル制御する必要が生じました。デジタル制御により、ミキサーの制御面から離れた場所にマイク・プリアンプを配置できるようになりました。これにより、スタジオや公演会場に敷設されていた重いアナログのマルチコア・ケーブルを、デジタル・オーディオを伝送する薄くて軽いネットワーク・ケーブルに置き換えるという、価値ある新しい製品アーキテクチャが実現されました。デジタル・ゲイン制御により、マイク・プリアンプ・ゲイン設定を保存し、ソフトウェアによる制御下で呼び出すことも可能になりました。これは今では、ミキシング・コンソールの機能として広く普及し、ラップトップ用の録音インターフェースなど、他のプロ仕様オーディオ製品でますます注目されています。

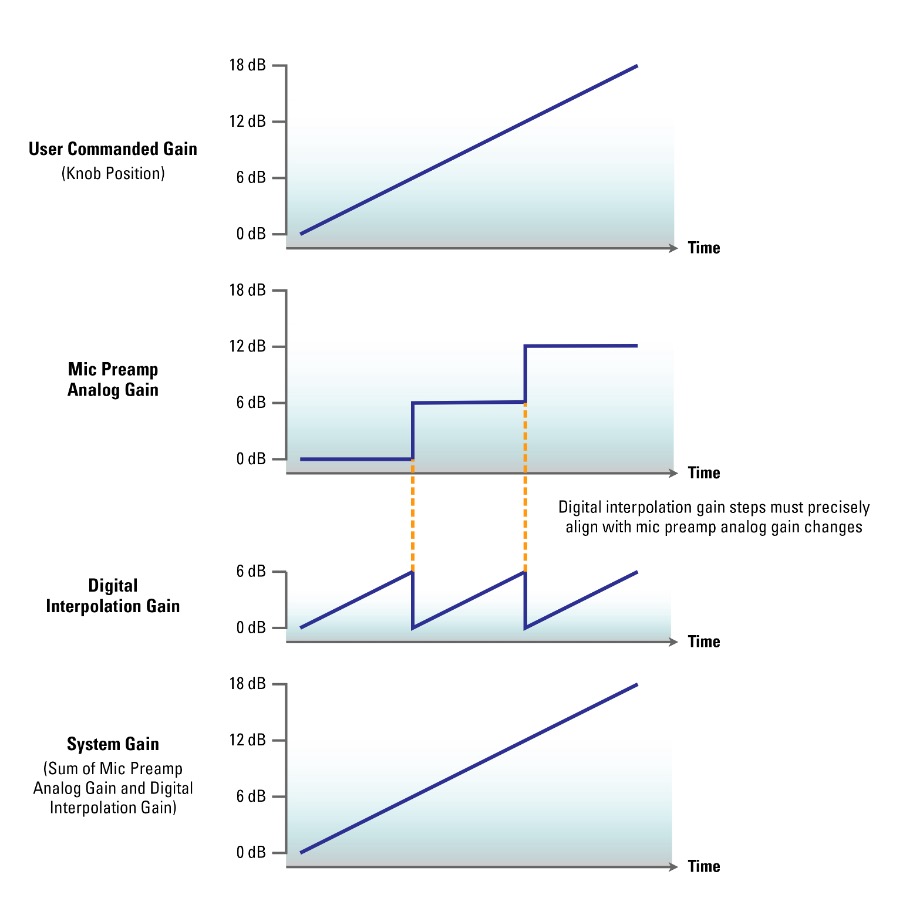

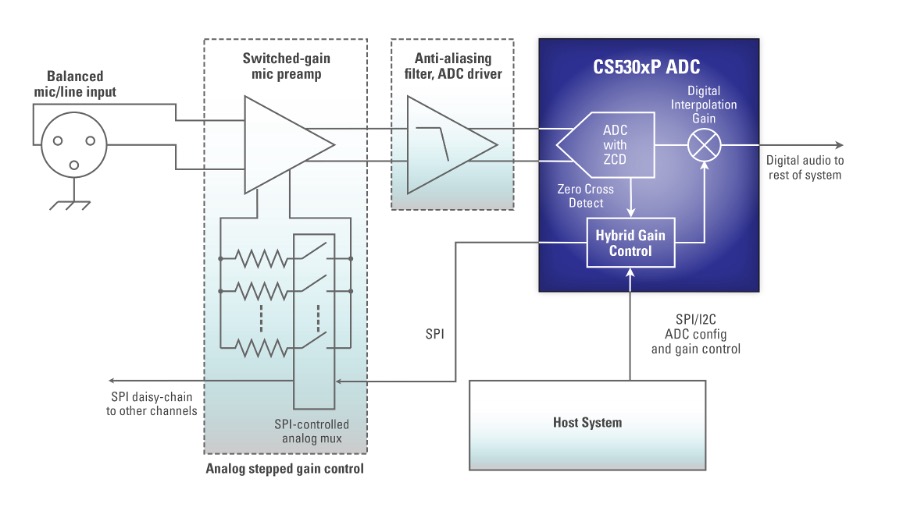

このデジタル・ゲイン制御は多くの場合、アナログ・マルチプレクサを使用して、さまざまなゲイン設定レジスタをマイク・プリアンプ回路に切り替える目的で実装されます。通常、制御面のユーザ・インターフェースは回転エンコーダで構成されています。サウンド・エンジニアは、このゲイン・ノブがポテンショメータの連続ゲイン応答で反応することをまだ期待しています。これを実現するために、制御ソフトウェアは、ADCの後に適用されるデジタル「補間ゲイン」を管理して、アナログ・ゲイン・ステップ間で補間します。サウンド・エンジニアがゲイン・ノブを時計回りに回すと、切り替えたマイク・プリアンプ・ゲインはステップ単位で増加し、デジタル・ゲインはステップ間でスムーズに補間します(図1)。

アナログ・ゲインが 1 ステップ増加すると、スムーズなゲイン増加を維持するために、デジタル・ゲインは同時に同じ量だけ減少する必要があります。アナログ・ゲインとデジタル・ゲインの合計はシステム・ゲインを生成するため、ノブが指令するゲインと同じ量にする必要があります。

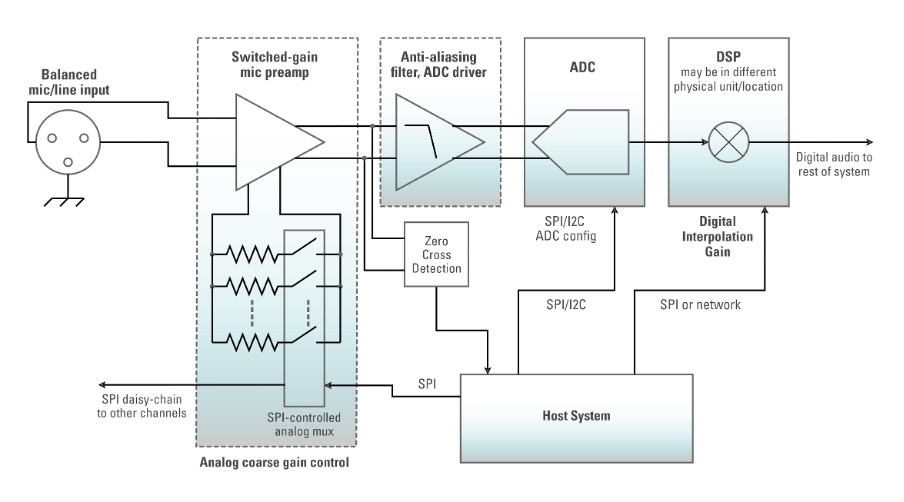

ゲイン変更時のポップノイズを最小限に抑えるために、アナログ・ゲインの変更では、信号のゼロ・レベル・ポイントを通過するアナログ信号とタイミングを合わせることもできます。これによって、信号振幅がゼロのときにゲイン変動が発生し、ゲイン変動が可聴過渡応答を引き起こすのを防ぐことができます。HGCなしでこのスキームを実装する典型的なシステムを図2に示します。

マイク・プリアンプ・ゲインのデジタル制御を実装することの難しさ

プロ仕様オーディオ製品の設計者は、図2に示すプリアンプ・ゲインのデジタル制御方式の実装において、長年にわたってさまざまな問題や複雑さに直面してきました。

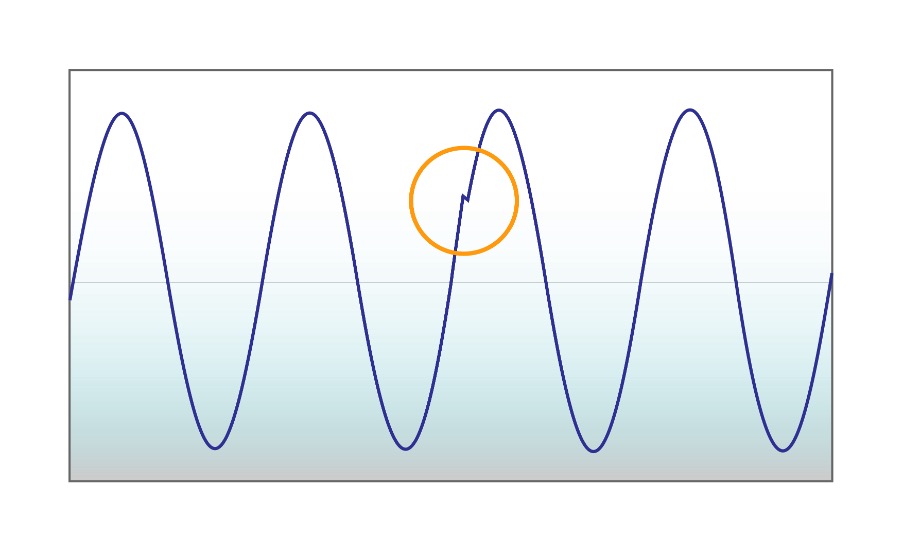

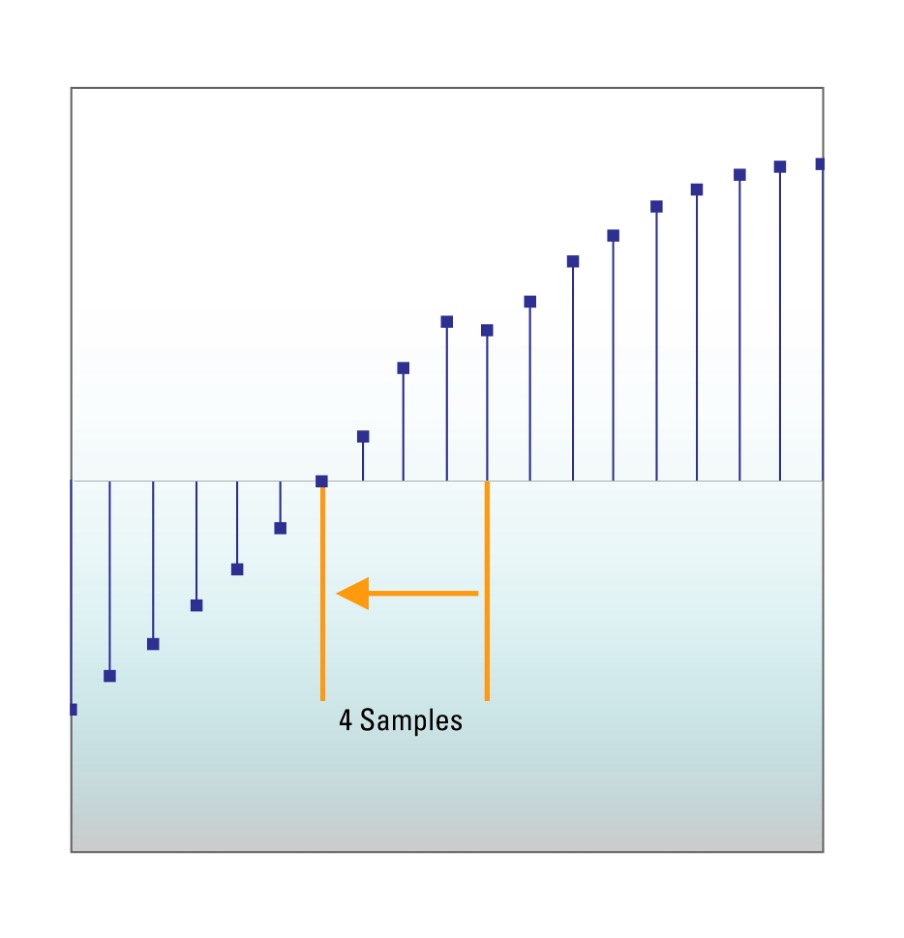

おそらく最大の問題は、通常はデジタル補間ゲインがオーディオ・システムのDSPに実装されることです。これは多くの場合、マイク・プリアンプとは異なるシステム部分で実行され、システムの制約により、アナログ・ゲインの変更とデジタル補間ゲイン・ステップとの間の正確な同期化を達成することが困難になる可能性があります。こうした動作間のタイミングのずれは、以下に示すように、Cirrus LogicのHGCデモ・ハードウェアを誤って構成することで、可聴過渡応答を引き起こす可能性があります。これらの図は、1kHzの正弦波でのアナログ+3dB増加および-3dBデジタル・ゲイン・ステップを含むゲイン変更を示しています。アナログ・ゲインの変更はゼロ交差ポイントと同時に発生しますが、デジタル・ゲインの整合ステップは4サンプル(約83μs)の遅れがあります。これにより、波形にグリッチがあり(図3および図4)、はっきりと聞こえます。

これらの過渡応答は、ユーザーがマイク・プリアンプ・ゲイン制御のノブを回すことによって発生するポップノイズのような音がします。ノブを速く回すと、急速な過渡応答の流れがジッパーのように聞こえます。いずれの場合も、これらのノイズは、システムがエミュレートするはずのポテンショメーターの挙動とは全く異なるため、サウンド・エンジニアにとっては気の散る、不快なものとなります。

もう1つの難点は、図2に示すシステムが複雑であることです。これには、アナログ・ゼロ交差検出用のディスクリート回路が含まれ、アナログ・ゲインの変動をゼロ交差と整合させて過渡現象を最小限に抑えます。省略すると、ポップノイズとジッパーノイズがはるかに強まり、ゲインを変更するときに、場合によってはオーディオ・チャンネルを一時的にミュートする必要があります。また、ホストからの複数の制御パスも必要です。DSPとアナログ入力パスが独立した2つの通信プロセッサの制御下にある場合、分散ホスト・ソフトウェアはシステム・ゲインの状態を2つのコンポーネントに分割し、それぞれを異なるコンピューティング・ノードに配置する必要があります。これにより、ソフトウェアの複雑さが大幅に高まる場合があります。

考えられる解決策の 1 つは、スイッチド・レジスタ・ゲインの選択の代わりに、乗算 DAC (MDAC) を使用することです。これにより、高解像度とポップフリーのゲイン変動が実現されますが、MDACデバイスは多くのプロ仕様オーディオ製品には高価すぎる可能性があります。あるいは、より多くのレジスタの組み合わせがあるマルチプレクサ・パスを増加させると、ステップ・サイズが小さくなり、連続ゲイン制御に近づけることができますが、これによってコストと複雑度が増加し、オーディオ性能が低下する場合があります。

つまり、デジタル制御されたマイク・プリアンプ・ゲインを実装すると、ゲイン変化時にポップノイズ/ジッパーノイズの影響を受やすくなるか、またはポップノイズ/ジッパーノイズを軽減するために高いコストと複雑さを選ぶかの、いずれかに迫られます。

Cirrus LogicCS530xP、ポップフリーのゲイン制御を容易に

Cirrus Logic CS530xPファミリーのプロ仕様オーディオADCは、HGCを導入し、マイク・プリアンプ・ゲインのポップフリーのデジタル制御を大幅に簡素化します。HGCは、図2に示すレガシー・システムのいくつかの要素をADCチップに統合することでこれを実現します。

設定可能なデイジーチェーンSPIコントローラは、最大8つのマイク・プリアンプのゲインを構成します。各ADCチャネルは、ポップフリーのアナログ・ゲイン変更を同期するアナログ・ゼロ交差検出器を備えています。各ADC信号経路には、ポテンショメータの連続制御の感触を模倣する補間ゲインを実装するためのデジタル・ゲイン制御が含まれています。HGCロジックは、上記の機能の動作をすべて調整し、正確に同期されたグリッチフリーのゲイン更新を実行します。HGCによる簡素化されたシステム・アーキテクチャを図5に示します。

ユーザーが制御面のゲイン制御ノブを回すと、ホスト・ソフトウェアはCS530xPのレジスタに値を書き込み、マイク・プリアンプ・ゲインの変更を設定して要求します。これにより、HGCはSPIを介してマイク・プリアンプを制御し、必要なゲイン変動を設定します。これは、アナログ・ゼロ交差と正確に調整されます。HGCはデジタル・オーディオ信号経路も制御できるため、デジタル・ゲインの変化とアナログ・ゲインの変化が正確に調整されます。ゼロ交差によるアナログ・ゲインとデジタル・ゲインの変化の正確な調整により、ポップフリーのゲイン更新が保証されます。

アナログ/ゲインおよびデジタル補間ゲインの状態は、どちらもCS530xP HGCブロックのレジスタ内にあり、ADCを制御する1つのホスト・プロセッサの管理下にあります。

図2に示すレガシー・システムと比較して、HGCシステムはよりシンプルなハードウェアを搭載しているため、部品表とソフトウェアがシンプルになり、ゲイン変更時にポップノイズとジッパーノイズを低減します。

ハイブリッド・ゲイン制御の仕組み

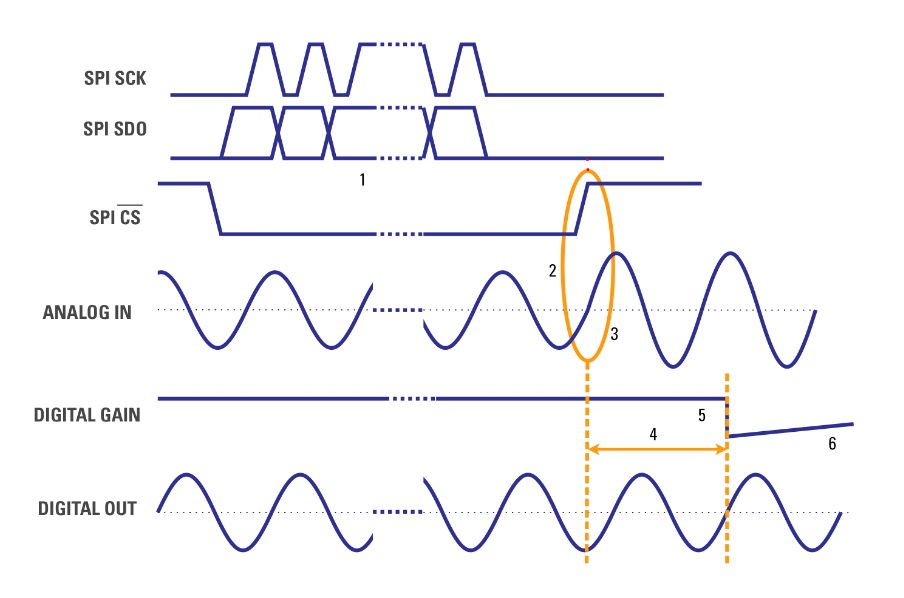

HGCによるゲイン変更のイベント・シーケンスを図6に示します。ゲインの変更は、ホスト・ソフトウェアがHGCレジスタに値を書き込み、ゲインの更新を設定およびトリガーすることで開始されます。これにより、HGC SPIインタフェースは、ゲイン・ビット・パターンをマイク・プリアンプのデイジーチェーンに送信し、1台のプリアンプを新たに指示されたゲイン値に設定します(図6のポイント 1参照)。ゲイン・ビット・パターンは、マイク・プリアンプの設計によって異なります。

HGC SPIインタフェースがゲイン・ビット・パターンをマイク・プリアンプにシフトした後、ゲインを変更しているチャネルでゼロ交差が検出されるまで(図6のポイント2)、SPI CSb信号は低アサートのままになります。これにより、CSbがデアサートされ、新しいゲイン・コードがマイクロフォン・プリアンプで有効になり、アナログ信号経路(図6のポイント3)でゼロ交差調整のゲインが瞬時に変化します。

ゲインの変更後、HGCはアナログ・アンチエイリアシング・フィルタ、ADC、およびデシメーション(間引き)フィルタを介して、マイク・プリアンプからの信号経路レイテンシを補正するために、構成可能な短い時間(通常は4~8サンプル期間、図6のポイント4)にわたり待機します。

この時点で、HGCは正確な時間設定のデジタル・ゲイン・ステップ(図6のポイント5)を実行し、アナログ・ゲインの変化に対抗します。その後、最終的な微調整ゲイン値に向けたゲイン・ランプを開始します(図6のポイント6)。数十ミリ秒かけて段階的にゲインを変更することで、可聴なトランジェントの発生を防ぎます。

既存のマイク・プリアンプ設計でポップフリー操作を実現

一部のプロ仕様オーディオ製品の設計者にとって、マイク・プリアンプの設計と音の特性は、重要なブランド資産であり、差別化できる機能です。HGCにより、製品の設計者は既存のマイク・プリアンプ設計でポップフリー動作を実現できます。マイク・プリアンプの設計は、次の3つのシンプルな要件に準拠している場合に使用できます。

ステップ状のゲイン制御を実行している。ゲイン・ステップは同じサイズである必要はなく、任意の値の任意の数のゲイン・ステップを使用できます。ゲインは、1つのマイク・プリアンプあたり1~32ビットの長さで、1つのSPIビット・パターンをデイジーチェーンSPIシフト・レジスタに書き込むことでゲインを変更できるように、デイジーチェーンSPIによって制御可能でなければなりません。HGCでは、SPIビット・パターンのゲイン値へのエンコーディングを完全に構成できます。ゲイン変更は、デイジーチェーンSPI 操作の終了時にSPI CSbをデアサートすると、すぐに有効にする必要があります。

シンプルでコンパクトな実装を実現するには、デイジーチェーン可能なSPI制御アナログ・マルチプレクサを使用して、異なる値のレジスタをマイク・プリアンプ回路に切り替えます。あるいは、8ビット74HCS595などの標準ロジック・シフト・レジスタをデイジーチェーンSPIと共に使用して、ポート拡張器と同様の方法で静的ロジック出力を提供することができます。これにより、アナログ・マルチプレクサを制御するか、またはディスクリート・トランジスタを直接制御することができます。

HGCは、ADCの各チャネル(Cirrus Logic CS5308Pの場合は、最大8チャネル)のマイク・プリアンプ・ゲイン制御をサポートしています。また、マイク・プリアンプ・ゲインと同じSPIインターフェイスを介して、最大64ビットの追加SPIデイジーチェーン・デバイスの制御も行います。これらは、追加のマイクロコントローラI/Oまたはシリアル・インターフェイスを必要とせずに、入力パスに関連付けられた補助ハードウェア機能の制御に使用できます。アプリケーションには、+48Vファントム電源の切り替え、アナログ・ハイパス・フィルタの有効化、入力コネクタによるLEDの制御、バランス入力とアンバランス入力の切り替えなどがあります。

既存のソフトウェア・アーキテクチャから簡単に制御

HGCによるゲイン変更の制御は、アナログ・ゲインとデジタル補間ゲインの両方がホスト・ソフトウェアによって計算および設定される既存のスキームと類似しています。つまり、HGCを使用するために必要なホスト・ソフトウェアの変更は、通常は軽微であり、範囲が限定されています。HGCゲイン変更を指令するために、ホスト・ソフトウェアはCS530xP ADCチップのHGCレジスタに4つの情報を書き込みます。

- ゲイン選択ビット・パターン:プリアンプの設計に従って、選択したアナログ・ゲインの値にマイク・プリアンプを設定するSPIビットのパターン。

- アナログ・ゲイン:選択されたマイク・プリアンプに対応する新しいビット・パターンの絶対アナログ・ゲイン値は、0.125dB単位で最も近い値に丸められます。デジタル・ゲイン:ユーザーが設定したシステム・ゲインを達成するために必要なデジタル補間ゲインの値は、0.125dB単位で最も近い値に丸めます。

- ゲイン更新信号:上記3つの項目がすべて書き込まれたことを示します。これにより、HGCが同期ゲイン変更を実行できるようになります。

以前のデジタル・ゲイン制御の実装と同様に、特定のシステム・ゲイン要求に対して選択するアナログ・ゲイン・ステップを選択するアルゴリズムは、ダイナミック・レンジを管理するシステム設計者の好みに応じてホスト・ソフトウェアに実装されます。

アナログ・ゲイン・レジスタのフィールドは、以前の設定と新しい設定の間のマイク・プリアンプにおけるアナログ・ゲインの差を決定するために使用されます。この差異は、アナログ・ゲイン・ステップに対抗するためにデジタル・ゲイン・ステップの大きさと方向を決定するために使用されます。その後、デジタル・ゲインがデジタル・ゲインのフィールドで指定された新しい値に向けて段階的に調整されます。

ホストはいつでもゲイン変更を命令することができ、アクティブなチャネルのおおよその数にゼロ交差タイムアウト構成設定(最大20ms)を掛けた時間範囲内で実行されることが保証されます。実際のオーディオ信号では、オーディオゼロ交差検出のために、それよりもはるかに速く実行される可能性があります。

HGCが長期にわたる設計上の課題を解決

Cirrus LogicのCS530xPADC製品ファミリー、およびその他のプロ仕様オーディオ製品のHGCにより、ポップノイズやジッパーノイズのない、スムーズで静かなゲイン変更でデジタル制御されたマイク・プリアンプを簡単に低コストで実装できます。これにより、マイク・プリアンプ・ゲインのデジタル制御の実装における長年にわたる設計上の課題が解決されます。これまでは、プロ仕様のオーディオ製品設計者にとって、ゲイン変更時の厄介なポップノイズとジッパーノイズ、または高い複雑性および大規模な部品表(BOM)の間で困難なトレードオフを迫られていました。

HGCによって、既存のスイッチド・ゲイン・マイク・プリアンプ設計でこれらの利点を簡単に実現し、既存のホスト・ソフトウェア・アーキテクチャから簡単に制御できます。ファントム電源、信号経路リレー、LEDなどの補助機能の統合制御など、マイク・プリアンプ・ゲイン制御のためのハードウェア設計が簡素化されます。この新しい機能は、わずか25mW/チャネルの消費電力で、123dBのダイナミック・レンジと少なくとも-110dB THD+Nの最先端のADC性能と簡単に統合できます(Cirrus Logic CS5308P)。

HGCによって、ポテンショメータのようなデジタル・マイク・プリアンプ・ゲイン制御を、ポップノイズやジッパーノイズなしで、すべてのプロ仕様オーディオ製品層に手頃な価格で優れたユーザー体験を提供するのが可能になります。

この記事は、2023年11月にaudioXpressで公開されました。